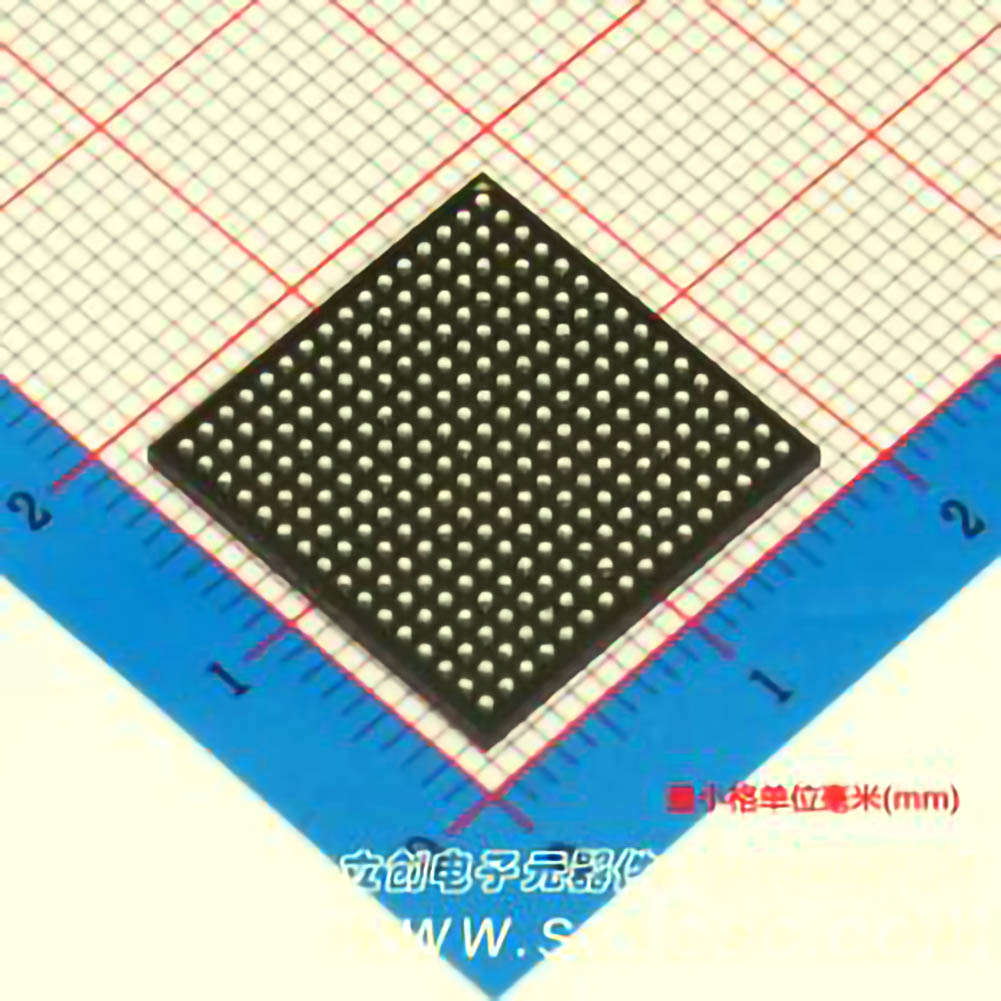

Application and performance optimization of EP4CE15F17C8N in FPGA circuit design

In the world of FPGA circuit design, achieving optimal performance while maximizing resource utilization is crucial. This article explores the application of the EP4CE15F17C8N , an FPGA from Intel's Cyclone IV series, focusing on practical approaches for enhancing performance and optimizing its application in various design scenarios. The piece breaks down both theoretical insights and practical tips for FPGA designers, making it an invaluable resource for professionals seeking to get the best out of their designs.

FPGA, EP4CE15F17C8N, performance optimization, FPGA design, circuit design, Intel Cyclone IV, resource utilization, design strategies, hardware acceleration, Embedded systems

Introduction to the EP4CE15F17C8N FPGA and Its Applications

The Intel/Altera FPGA (Field-Programmable Gate Array) has revolutionized hardware design by offering customizable logic circuits that can be reprogrammed to meet the specific requirements of any application. Among the various FPGA offerings, the EP4CE15F17C8N stands out due to its unique combination of cost-effectiveness, versatility, and performance. This device is part of Intel's Cyclone IV series, which is renowned for its ability to balance performance and power consumption, making it a perfect choice for embedded systems, Communication , industrial automation, and other demanding applications.

Understanding EP4CE15F17C8N FPGA Features

The EP4CE15F17C8N is built on Intel's advanced 40nm process technology, which offers a good mix of power efficiency and processing capability. It boasts 15,000 logic elements (LEs), 504Kbits of embedded Memory , and multiple high-speed I/O pins. These features make it highly suitable for applications requiring moderate logic density and performance but without the excessive cost or complexity of higher-end FPGAs.

One of the key selling points of the EP4CE15F17C8N is its low power consumption, which allows it to perform intensive operations while maintaining minimal thermal output. This is particularly important in embedded systems where power budgets and heat dissipation are critical factors.

Common Applications of EP4CE15F17C8N

Due to its balanced features, the EP4CE15F17C8N is widely used in a variety of applications:

Embedded Systems: The FPGA's flexibility makes it ideal for embedded processing, such as controlling sensors, processing data streams, and managing communication protocols.

Signal Processing: The FPGA excels at handling real-time signal processing tasks like filtering, modulation, and data conversion.

Communication Systems: With its ability to handle high-speed data transfer, the EP4CE15F17C8N is well-suited for use in communication protocols such as Ethernet and PCIe.

Industrial Automation: The low power consumption and fast processing speeds make this FPGA a good fit for automated systems in robotics and factory automation.

Automotive Systems: Used in advanced driver-assistance systems (ADAS) and in-car infotainment systems, where both performance and energy efficiency are key.

Performance Optimization Techniques for EP4CE15F17C8N

While the EP4CE15F17C8N offers solid base performance, the key to unlocking its full potential lies in effective performance optimization strategies. These strategies ensure that the FPGA meets specific application requirements without overburdening system resources or incurring unnecessary costs.

1. Efficient Resource Allocation and Pipelining

One of the most powerful features of FPGA design is the ability to implement custom hardware circuits tailored for specific tasks. When designing for the EP4CE15F17C8N, it's crucial to make efficient use of the available logic elements and embedded memory blocks. Optimizing resource allocation helps prevent wasting hardware resources, ensuring that the FPGA can execute tasks at optimal speed without consuming excessive power.

Pipelining is a key technique for performance optimization in FPGA design. By breaking down complex tasks into smaller stages and allowing these stages to process concurrently, pipelining maximizes throughput while maintaining a relatively low latency. This approach is particularly useful for high-speed operations like signal processing and data conversion, where continuous throughput is essential. Implementing pipelining efficiently on the EP4CE15F17C8N requires careful consideration of Clock cycle Timing and resource usage, so that stages are balanced and do not result in excessive delays or wasted logic.

2. Timing Closure and Clock Domain Management

Achieving timing closure is essential for any FPGA design, ensuring that the system operates at the desired clock speed without timing violations. In FPGA-based systems like the EP4CE15F17C8N, timing constraints must be met for all paths within the design to ensure reliable operation. Timing closure refers to the successful arrangement of logic gates, registers, and interconnects so that signals arrive at their destinations within the allowable time frame.

For optimal performance, designers must manage clock domains effectively. The EP4CE15F17C8N allows multiple clock domains to operate independently, but careful planning is needed to ensure that clock crossings are handled without errors. Techniques such as clock synchronization and FIFO buffers are essential in designs with multiple clock domains to prevent data corruption and ensure seamless operation.

3. Power Management and Dynamic Voltage Scaling

One of the biggest challenges in FPGA design, particularly in embedded and mobile applications, is managing power consumption. The EP4CE15F17C8N, being a low-power device, provides designers with several tools to minimize energy usage while maintaining high performance.

Dynamic voltage and frequency scaling (DVFS) is one of the most effective strategies to manage power. This technique adjusts the voltage and frequency of the FPGA depending on the workload, reducing power consumption during periods of low activity and boosting performance during high-demand operations. For the EP4CE15F17C8N, implementing power gating on unused logic blocks or transitioning to lower power states when not in use can significantly reduce the overall system power consumption.

4. Memory Optimization and Data Path Design

Efficient memory utilization is crucial for performance optimization. The EP4CE15F17C8N includes embedded memory blocks that can be used for data storage, such as FIFOs and lookup tables. Optimizing these memory elements ensures faster data access and reduces bottlenecks in data-heavy applications like real-time signal processing or communications.

Data path optimization refers to the design of the internal circuitry that facilitates data flow between components. A well-designed data path minimizes the number of clock cycles required for data transfer, enhancing overall system throughput. For the EP4CE15F17C8N, effective data path design can be achieved by using efficient routing strategies, minimizing cross-talk, and making use of the FPGA’s built-in multiplexers and bus structures.

5. Leveraging Hardware Accelerators

One of the greatest advantages of FPGAs is their ability to offload computationally heavy tasks from general-purpose processors, a feature known as hardware acceleration. The EP4CE15F17C8N's architecture supports custom hardware accelerators, which can significantly speed up operations such as matrix multiplication, encryption, or data compression. By implementing parallel processing with hardware accelerators, designers can achieve much higher throughput compared to software-based solutions, while also saving on power consumption.

Integrating accelerators requires careful consideration of the FPGA’s resources, especially the balance between logic elements and embedded memory. Effective use of hardware accelerators can vastly improve performance in applications requiring intensive data processing, such as video processing, machine learning, or scientific computations.

Conclusion

The EP4CE15F17C8N FPGA provides an excellent platform for a wide range of applications, from embedded systems to communication infrastructure. By employing a mix of resource-efficient design, timing closure techniques, and power management strategies, FPGA designers can unlock the full potential of this versatile device. Whether it is in reducing latency, optimizing power consumption, or accelerating complex computations, the EP4CE15F17C8N offers a robust framework for achieving high-performance designs.

For designers aiming to maximize the performance of their EP4CE15F17C8N-based circuits, the key lies in understanding and implementing best practices for resource utilization, timing optimization, and power management. By adopting the right design methodologies, the EP4CE15F17C8N can help drive innovation in fields as diverse as industrial automation, telecommunications, and embedded processing. As the demand for high-performance, low-power devices continues to grow, mastering the optimization of the EP4CE15F17C8N will become increasingly essential for FPGA designers looking to stay ahead in this competitive field.

Partnering with an electronic components supplier sets your team up for success, ensuring the design, production, and procurement processes are quality and error-free.